# ORIGINAL PAPER

# Biological Cybernetics

# A comprehensive workflow for general-purpose neural modeling with highly configurable neuromorphic hardware systems

Daniel Brüderle · Mihai A. Petrovici · Bernhard Vogginger · Matthias Ehrlich · Thomas Pfeil · Sebastian Millner · Andreas Grübl · Karsten Wendt · Eric Müller · Marc-Olivier Schwartz · Dan Husmann de Oliveira · Sebastian Jeltsch · Johannes Fieres · Moritz Schilling · Paul Müller · Oliver Breitwieser · Venelin Petkov · Lyle Muller · Andrew P. Davison · Pradeep Krishnamurthy · Jens Kremkow · Mikael Lundqvist · Eilif Muller · Johannes Partzsch · Stefan Scholze · Lukas Zühl · Christian Mayr · Alain Destexhe · Markus Diesmann · Tobias C. Potjans · Anders Lansner · René Schüffny · Johannes Schemmel · Karlheinz Meier

Received: 10 November 2010 / Accepted: 19 April 2011 / Published online: 27 May 2011 © Springer-Verlag 2011

**Abstract** In this article, we present a methodological framework that meets novel requirements emerging from upcoming types of accelerated and highly configurable neuromorphic hardware systems. We describe in detail a device with 45 million programmable and dynamic synapses that is currently under development, and we sketch the conceptual challenges that arise from taking this platform into opera-

D. Brüderle (⊠) · M. A. Petrovici · B. Vogginger · T. Pfeil ·

S. Millner · A. Grübl · E. Müller · M.-O. Schwartz ·

D. H. de Oliveira · S. Jeltsch · J. Fieres · M. Schilling · P. Müller ·

O. Breitwieser · V. Petkov · J. Schemmel · K. Meier

Kirchhoff Institute for Physics, Ruprecht-Karls-Universität

Heidelberg, Heidelberg, Germany

e-mail: bruederle@kip.uni-heidelberg.de

Present Address: M. Schilling Robotics Innovation Center, DFKI Bremen, Bremen, Germany

L. Muller · A. P. Davison · A. Destexhe Unité de Neuroscience, Information et Complexité, CNRS, Gif sur Yvette, France

M. Diesmann RIKEN Brain Science Institute and RIKEN Computational Science Research Program, Wako-shi, Japan

# M. Diesmann

Bernstein Center for Computational Neuroscience, Universität Freiburg, Freiburg, Germany

M. Ehrlich · K. Wendt · J. Partzsch · S. Scholze · L. Zühl · C. Mayr · R. Schüffny Institute of Circuits and Systems, Technische Universität Dresden, Dresden, Germany

J. Kremkow

Bernstein Center Freiburg, University of Freiburg, Freiburg, Germany

tion. More specifically, we aim at the establishment of this neuromorphic system as a flexible and neuroscientifically valuable modeling tool that can be used by non-hardware experts. We consider various functional aspects to be crucial for this purpose, and we introduce a consistent workflow with detailed descriptions of all involved modules that implement the suggested steps: The integration of the hardware interface into the simulator-independent model description language PyNN; a fully automated translation between the PyNN domain and appropriate hardware configurations; an executable specification of the future neuromorphic system that can be seamlessly integrated into this biology-to-hardware mapping process as a test bench for all software layers and possible hardware design modifications; an evaluation scheme that deploys models from a dedicated benchmark library, compares the results generated by virtual or prototype hardware devices with reference software simulations and analyzes the differences. The integration of these components into one hardware-software workflow provides an ecosystem for ongoing preparative studies that support the hardware design process and represents the basis for the maturity of the model-to-hardware mapping software.

P. Krishnamurthy · M. Lundqvist · A. Lansner Computational Biology, KTH Stockholm, Stockholm, Sweden

E. Muller

Brain Mind Institute, Ecoles Polytechniques Federales de Lausanne, Lausanne, Switzerland

T. C. Potjans Institute of Neuroscience and Medicine (INM-6), Research Center Jülich, Jülich, Germany

T. C. Potjans RIKEN Computational Science Research Program, Wako-shi, Japan The functionality and flexibility of the latter is proven with a variety of experimental results.

**Keywords** Neuromorphic · VLSI · Hardware · Wafer scale · Software · Modeling · Computational neuroscience · PyNN

# **1** Introduction

# 1.1 Neuroscience and technology

Advances in neuroscience have often gone hand in hand with significant progress in the applied technologies, tools, and methods. While the experimental investigation of living neural tissue is indispensable for the generation of a detailed knowledge base of the brain, from which understanding of underlying principles can emerge, technological difficulties have always imposed limits to this endeavor. Until today it is not possible to study relevant observables in a sufficiently large fraction of brain tissue under realistic conditions and with a spatiotemporal resolution that is high enough to fully capture—and possibly consistently explain—the mechanisms of higher-order brain functions.

Therefore, in neuroscience, like in any other research field on dynamical systems that cannot be fully explored by experimental methods, models represent an indispensable approach to test hypotheses and theories on the real subject of interest. However, even neural modeling is significantly constrained and influenced by the set of available technologies. The spectrum of feasible experimental setups, in particular in computational neuroscience, directly depends on the accessible computational power. The difficulty of efficiently mapping the massive parallelism of neural computation in biological tissue to a limited number of digital general purpose CPUs is a crucial bottleneck in the development of large-scale computational models of neural networks, where statistics-intensive analyses or long-term observations of network dynamics can become computationally extremely expensive (see e.g., Morrison et al. 2005, 2007; Brette et al. 2006).

#### 1.2 Neuromorphic hardware

For an alternative modeling approach, the so-called *neuromorphic engineering*, the technology-driven nature is even more obvious. In a physical, typically silicon form, neuromorphic devices mimic the structure and emulate the function of biological neural networks. This branch of neuroscience has its origins in the 1980s (Mead and Mahowald 1988; Mead 1989, 1990), and today an active community is working on analog or mixed-signal *VLSI*<sup>1</sup> models of neural systems (for reviews, see e.g., Renaud et al. 2007; Indiveri et al. 2009).

Dedicated implementations of said computational models are typically more power efficient compared to general purpose architectures and are well suited for e.g., embedded controllers of autonomous units like robots. Fault tolerance features observed in biological neural architectures are expected to apply to corresponding neuromorphic hardware implementations as well. This fact can offer one important way to create reliable computing components on the basis of future nano-scale hardware constituents, where current design strategies will run into serious yield problems. Moreover, the inherent parallelism of on-chip emulation of neural dynamics has the potential to overcome the aforementioned scaling limitations of pure software simulations.

Still, until today the focus of neuromorphic projects is mostly very application-specific. The majority of groups is working on neuromorphic sensors like e.g., silicon retinas and visual processing systems (Netter and Franceschini 2002; Delbrück and Liu 2004; Serrano-Gotarredona et al. 2006; Merolla and Boahen 2006; Fu et al. 2008; Gomez-Rodriguez et al. 2010) or motor control in robotics (Lewis et al. 2000). The requirement of communication with the environment is one important reason for the fact that nearly all neuromorphic devices reported so far are designed to operate in real time. However, even the projects that deal with mimicking, studying or applying neural information processing (Vogelstein et al. 2007), self-organization (Häfliger 2007; Mitra et al. 2009), or even hybrid setups coupling neuromorphic devices with living tissue (Bontorin et al. 2007) are usually focused on one type of neural architecture, one anatomical region, or one function the implemented network is supposed to fulfill.

Two main reasons for this self-limitation of neuromorphic development are the finite size of every neuromorphic device as well as the limited possibilities to change the behavior of individual cells and the network connection patterns once they have been cast into silicon. A typical approach to reduce size limitations is to scale up networks by inter-connecting multiple hardware modules (Costas-Santos et al. 2007; Berge and Häfliger 2007; Indiveri 2008; Schemmel et al. 2008). Furthermore, recent advances in neuromorphic development eventually promise to overcome the limited flexibility of hardware models by offering a sufficiently fine-grained configurability of both the neuron parameter values as well as the network connectivity (Indiveri et al. 2006, 2009; Schemmel et al. 2007, 2008, 2010; Ehrlich et al. 2007). This crucial feature allows to consider the utilization of neuromorphic systems as flexible modeling tools to approach open neuroscientific questions with new strategies (Kaplan et al. 2009; Brüderle et al. 2009, 2010; Brüderle 2009).

<sup>&</sup>lt;sup>1</sup> Very large scale integration.

#### 1.3 A novel methodological approach

The FACETS<sup>2</sup> research project (FACETS 2010) and its successor BrainScaleS (BrainScaleS 2010) aim at a comprehensive exploitation of the possibilities inherent to that approach. The highly interdisciplinary collaborations gather neurophysiological, theoretical, and hardware expertise in order to develop and operate a large-scale neuromorphic device that can serve as a flexible neural network emulation platform with hitherto unattained configurability and acceleration. It is planned to exploit this combination of features with experimental paradigms that are not realizable with pure software simulations, like long-term learning studies, systematic parameter explorations, and the acquisition of statistics for every tested setup.

Following this attempt, one important insight has emerged that has only rarely been addressed in the literature so far (exceptions are e.g., Dante et al. 2005; Oster et al. 2005): Any hardware device that is complex enough to serve as a useful neural modeling tool is useless without an appropriate software environment that implements a reasonable methodological framework for its operation. For any developed neuromorphic modeling platform, hard- and software have to form a functional unit. Moreover, the need for methods that have to be applied in order to make the advantages of a neuromorphic device accessible to non-hardware experts does not only refer to the actual *operation* of the device itself. Instead, already its *design process* needs to be supported and influenced by preparatory studies, e.g., with virtual versions of the future hardware–software system.

In this publication, we summarize the FACETS efforts to create a comprehensive methodological framework providing a workflow aiming to make the innovative FACETS wafer-scale hardware system a generic modeling tool that is applicable to a wide range of neuroscientific questions and accessible to the neuroscientific community.

# 1.4 Structure of this article

This introduction is followed by a description of the complete neuromorphic modeling infrastructure. This includes both the utilized hardware devices and the *workflow* that is in focus of this article, i.e., the framework of methods and software modules that have been developed for the design assistance, the benchmarking and the actual operation of the platform. A third section presents data and results that provide a proof of functionality for the concept as a whole. Various components of the workflow are evaluated, and the performance of benchmark model experiments performed with the complete system is studied and analyzed. The last section discusses the state of validation of the presented framework as well as its advantages and limitations considering alternative approaches. Implications and plans for future work and new perspectives arising from the presented achievements are outlined.

# 2 The workflow components: modules and methods

The following section provides an overview over the complete infrastructure that has been developed to realize a novel neural modeling concept built around the FACETS neuromorphic hardware system. For this purpose, the neuromorphic device itself is presented in Sect. 2.1 on a level of detail that is appropriate to the method descriptions that follow. These methods are either implemented by or directly rely on an innovative software framework, which will be explained in Sect. 2.2 by means of its structure and concepts. A significant achievement for the targeted design and development of a harmonizing hardware–software unit forming the modeling platform was the collection of a set of literature-based benchmark model experiments, as summarized in Sect. 2.4.

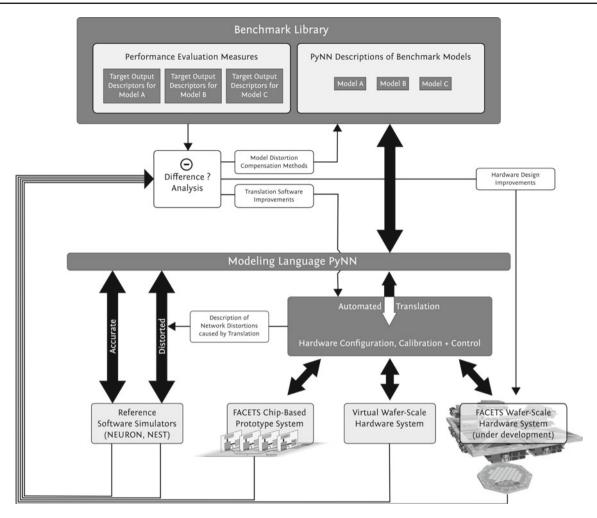

The workflow that has been developed around these three main components is schematically depicted in Fig. 1: The library of dedicated neuroscientific benchmark models, including descriptions and measures to evaluate their correct functionality, has been established by members of the FACETS research project (FACETS 2010). For any model from within this set, a description on the basis of the simulator-independent modeling language PyNN (see Sect. 2.2.1) is available. The mentioned translation software stack performs an automated conversion of these scripts into appropriate data for the configuration and control of different hardware or software back-ends. The same stack also re-translates the resulting hardware output into the domain of its biological interpretation. During the development and optimization phase of the FACETS wafer-scale hardware system, an elaborate virtual version of the device (see Sect. 2.3) serves as a test bench for the development and tuning of all involved translation software modules.

In addition to the virtual wafer-scale device, a purely chipbased neuromorphic system (see Sect. 2.1.5) provides important information about characteristics of circuits planned to be implemented in the wafer-scale system. These ASICs thereby support the wafer-scale design process and the development of possible strategies to compensate unavoidable phenomena like transistor-level variations or noise. The outputs of all applied hardware or virtual hardware back-ends are compared with the target output descriptions included with the models in the benchmark library and with reference experiments on pure software simulators. The remaining differences are analyzed, as is exemplarily presented in Sect. 3.1.

In an ongoing optimization flow, the benchmark models are repeatedly mapped to the still evolving hardware

<sup>&</sup>lt;sup>2</sup> Fast analog computing with emergent transient states.

Fig. 1 Optimization workflow toward neural modeling with neuromorphic hardware devices. The main components are 1. the highly configurable FACETS neuromorphic hardware devices, 2. the software module stack that performs an automated translation of neural network experiments described with the modeling language PyNN into corre-

substrate with the likewise continuously optimized software framework. The iteratively applied result analyses provide the fundament for improvements that close the workflow loop: The hardware design, the biology-to-hardware translation modules and optionally even the models themselves are modified such that the functional effects of remaining distortions caused by the model-to-hardware mapping process are minimized.

Hence, the first application of the presented workflow is to take novel types of hardware devices into operation. Furthermore, it can serve as a basic methodological paradigm for the actual target application of neuromorphic systems, i.e., the exploration and optimization of neural architectures by means of different optimization objectives. These include the search for computationally powerful structures or for setups that can reproduce biologically plausible dynamics.

While this section motivates and explains the workflow *as a whole* and provides descriptions of all involved components

sponding hardware configuration and control patterns, and 3. a benchmark library that contains a collection of neuroscientific models written in PyNN. For a detailed explanation of the complete flow and all individual steps and components see full text

and methods, the scope of this article would be exceeded by providing detailed motivation for *all* particular choices of methods and components being part of the framework. The reasons for individual methodological or design decisions can be found in the literature referenced within the corresponding paragraphs.

# 2.1 The FACETS hardware system

In the following, the FACETS wafer-scale hardware system will be described with focus on conceptual and technical details that are relevant in the context of this article. More information on the hardware setup and circuitry can be found in Schemmel et al. (2008, 2010), Ehrlich et al. (2007), and Millner et al. (2010).

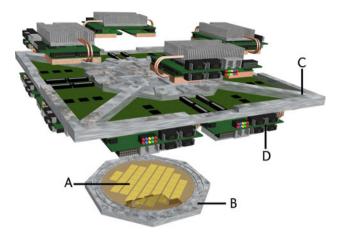

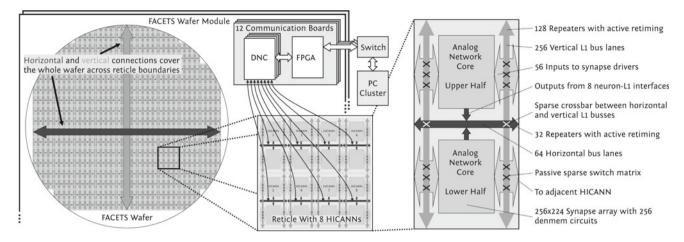

At the core of the FACETS wafer-scale hardware system (see Fig. 2) is an uncut wafer built from mixed-signal

Fig. 2 The FACETS wafer-scale hardware system: Wafer (A) comprising HICANN building blocks and on-wafer communication infrastructure, wafer bracket (B), top frame (C) and digital inter-wafer and wafer-host communication modules (D)

ASICs,<sup>3</sup> named *High Input Count Analog Neural Network* chips (*HICANNs*, Schemmel et al. 2008) that provide a highly configurable substrate which physically emulates adaptively spiking neurons and dynamic synapses. The intrinsic time constants of these VLSI model circuits are multiple orders of magnitude shorter than their biological originals. Consequently, the hardware model evolves with a speedup factor of  $10^3$  up to  $10^5$  compared to biological real time, the precise value depending on the configuration of the system.

In addition to a high-bandwidth asynchronous on-wafer event communication infrastructure, full custom digital offwafer ASICs provide terminals for a packet-based multi-purpose communication network (Scholze et al. 2010). These so-called *Digital Network Chips (DNCs)* are backed by a flexible FPGA<sup>4</sup> design that handles the packet routing (Hartmann et al. 2010). The communication infrastructure is illustrated in Fig. 5. See Sect. 2.1.3 for details on the interchip communication scheme.

A full wafer system will comprise 384 interconnectable HICANNs, each of which implements more than 100,000 programmable dynamic synapses and up to 512 neurons, resulting in a total of approximately 45 million synapses and up to 200,000 neurons per wafer. The exact number of neurons depends on the configuration of the substrate, which allows to combine multiple neuron building blocks to increase the input count per cell.

# 2.1.1 Composition of the FACETS hardware system

The wafer as the main component for the FACETS waferscale hardware system has to be embedded into a framework

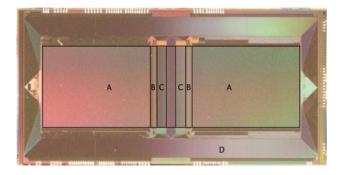

**Fig. 3** A photograph of the HICANN building block with synapse arrays (A), neurons (B), floating-gate arrays (C), and L1 routing (D)

that provides the electrical integration as well as the mechanical stability. The wafer has a diameter of 20 cm and will be placed into an aluminum plate which also serves as a heat sink. A multi-layer printed circuit board (PCB) is placed on top of the wafer. This PCB has to provide the fan-out of 1,500 impedance-controlled differential pairs and—in the worst case—has to deliver a total electrical power of 1,000 W to the wafer. A 14-layer fine pitch board with laser drilled microvias and a total size of  $430 \times 430$  mm meets these requirements. The PCB will be clamped to an aluminum frame that is also used as a platform for communication devices such as the 48 DNCs and the 12 FPGA boards (see Sect. 2.1.3). Figure 2 shows a 3-D drawing of the hardware composition. All depicted electrical and mechanical components are custom-made by FACETS project members.

# 2.1.2 The HICANN building block

The HICANN building block shown in Fig. 3 is the neuromorphic ASIC of the FACETS wafer-scale hardware system. The inter-chip communication scheme is explained in Sect. 2.1.3.

Simplifying, the HICANN can be divided into four parts: the neuron circuits with their analog parameter storage based on floating-gate technology (Lande et al. 1996), an array of 114,688 dynamic synapses and the Layer 1 (L1) bus system interconnecting HICANNs on a wafer. The hardware neurons implemented by the HICANN building blocks (Millner et al. 2010) can emulate the adaptive exponential integrateand-fire neuron model (AdEx, Brette and Gerstner 2005) which can produce complex firing patterns observed in biology (see e.g., Markram et al. 2004; Destexhe 2009), like spike-frequency-adaptation, bursting, regular spiking (RS), irregular spiking and transient spiking, by tuning a limited number of parameters (Naud et al. 2008). The decision to implement this particular neuron model in hardware was motivated by the large spectrum of possible and biologically relevant cell behavior realizable with a comparably compact circuitry. The latter fact is a crucial aspect when aiming at the

<sup>&</sup>lt;sup>3</sup> Application-specific integrated circuit.

<sup>&</sup>lt;sup>4</sup> Field programmable gate array.

integration of large numbers of neurons in one hardware system. For a neuromorphic implementation of Hodgkin-Huxley cells that consume significantly more chip area see e.g., Daouzli et al. (2008).

The model can be described by the following two differential equations for the membrane voltage V and the adaptation variable w and a reset condition specified further below:

$$-C_{\rm m}\frac{\mathrm{d}V}{\mathrm{d}t} = g_{\rm l}(V - E_{\rm l}) - g_{\rm l}\Delta_{\rm t}e^{\left(\frac{V - V_{\rm l}}{\Delta_{\rm t}}\right)} + w$$

$$+g_{\rm e}(t)(V - E_{\rm e})$$

$$+g_{\rm i}(t)(V - E_{\rm i}), \tag{1}$$

$$-\tau_{\rm w}\frac{\mathrm{d}w}{\mathrm{d}t} = w - a(V - E_1). \tag{2}$$

$C_{\rm m}$ ,  $g_{\rm l}$ ,  $g_{\rm e}$ , and  $g_{\rm i}$  are the membrane capacitance, the leakage conductance and the conductances for excitatory and inhibitory synaptic inputs, where  $g_{\rm e}$  and  $g_{\rm i}$  depend on time and on the inputs from other neurons.  $E_{\rm l}$ ,  $E_{\rm i}$ , and  $E_{\rm e}$  are the leakage reversal potential and the synaptic reversal potentials. The parameters  $V_{\rm t}$  and  $\Delta_{\rm t}$  are the effective threshold potential and the threshold slope factor. The time constant of the adaptation variable is  $\tau_{\rm w}$ . The adaptation parameter *a* has the dimension of a conductance.

If the membrane voltage crosses a certain threshold voltage  $\Theta$ , the neuron is reset:

$$V \to V_{\text{reset}},$$

(3)

$$w \to w + b. \tag{4}$$

The parameter b is responsible for spike-triggered adaptation.

A neuron can be constructed out of up to 64 so-called *denmem* circuits, each implementing the dynamics of the AdEx model and being connected to up to 224 synapses. This way a neuron could have synaptic inputs from up to 14,336 other cells. In addition, depressing and facilitating mechanisms of short-term synaptic dynamics (for a review, see Zucker and Regehr 2002) are implemented. A purely chip-based FAC-ETS hardware implementation of this feature is described and applied in Bill et al. (2010).

A general limitation of neuromorphic implementations of cell models is the fact that configurable parameter values will always have limited ranges. The value ranges of all AdEx parameters configurable in the hardware implementation have been designed such that the complete set of biologically relevant firing patterns distinguished, e.g., in Naud et al. (2008) can be reproduced. If this design goal was fully achieved is currently studied with HICANN prototypes, i.e., work in progress (see also Sect. 3.4).

2.1.2.1 Hebbian Learning in the FACETS Hardware Longterm Hebbian learning in the FACETS hardware devices is implemented in every synapse as spike-timing-dependent plasticity (STDP, reviewed e.g., in Morrison et al. 2008). To ensure high flexibility in terms of mappable neuronal networks each neuron in hardware needs an appropriate number of synaptic inputs. However, due to limited die area, a tradeoff between the number of synapses and the chip resources for a single synapse has to be made.

To achieve a minimal circuit size for the synapses, local correlation measurements and the local synaptic weight storage are separated from global weight update controllers (Schemmel et al. 2006, 2007). Causal and acausal correlations between pre- and post-synaptic spikes determine the temporal factor of the STDP rule described in Schemmel et al. (2004) and are accumulated locally until they are processed by the update controller. Synaptic weights are stored locally as digital values with a 4-bit resolution each. This resolution is again a trade-off between precision and chip resources and requires several correlated events to reach the next discrete weight value. If a sufficient amount of correlations is accumulated, the discrete weight is updated by the update controller. Since many synapses share one update controller a weight update is performed periodically with a frequency that has an upper limit determined by the circuitry (Schemmel et al. 2006). Since a reduced symmetric nearest-neighbor spike pairing scheme turned out to be one feasible approach for describing biological measurements (Burkitt et al. 2007; Morrison et al. 2008), this specific plasticity mechanism has been chosen to be implemented in hardware to further reduce the size of a synapse. Update controllers are modifying the synaptic weights by using look-up tables that are listing, for each discrete weight value, the resulting weight values in case of measured causal or acausal correlations. These lookup tables can be adapted to the weight-dependent factor of any STDP rule.

Despite its global weight update controllers, the STDP mechanism of the FACETS hardware has to be considered local to every synapse. The implementation of this particular model represents a project-wide decision on the most promising mechanism to be cast into silicon, taken in the early phase of FACETS. Recent developments in the modeling of learning and self-organization in neural networks (see e.g., Sjöström et al. 2008; Pfeiffer et al. 2010) combine such local rules with various global mechanisms like the reward-based modulation of large groups of synapses. With respect to more complex and relevant plasticity mechanisms, an extension to STDP rules with additional input parameters, e.g., membrane potentials, spike rates or global reward signals, is currently under development.

2.1.2.2 Parameter memories In contrast to most other systems, the FACETS wafer-scale hardware deploys analog floating-gate memories similar to cells developed by Lande et al. (1996) as storage devices for the analog parameters. Due to the small size of these cells, most parameters can be provided individually for a single neuron circuit. This way,

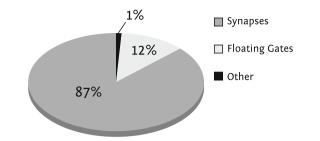

**Fig. 4** Sector diagram of the parameter space to configure one HIC-ANN chip. For a full wafer, the configuration data volume is 44 MB large

matching issues can be counterbalanced, and different types of neurons can be implemented on a single chip.

As a starting point for the parameter ranges, parameters from Brette and Gerstner (2005) and Destexhe et al (1998) have been used. The chosen ranges allow leakage time constants  $\tau_{mem} = C_m/g_1$  at an acceleration factor of 10<sup>4</sup> between 1 and 588 ms and an adaptation time constant  $\tau_w$  between 10 ms and 5 s in terms of biological real time. The parameters used by Pospischil et al. (2008), for example, lie easily within this range.

A substantial amount of digital memories is integrated in the chip, dominated by the synapse RAM. Each of the 114,688 synapses has 8 bit memory cells for weight and address storage. For the whole wafer, the synapse RAM alone is 38 MB large. Figure 4 shows the partitioning of the parameter memory on a HICANN building block. To compare the analog floating gates to normal digital memory, each cell has been counted as 10 bit, since this is the number of bits needed to program it.

#### 2.1.3 Communication infrastructure

The communication infrastructure of the FACETS waferscale hardware is illustrated in Fig. 5. Pulse communication is generally based on the digital transmission of neural events representing action potentials, but a distinction in two network layers can be made. An asynchronous, serial protocol, named Layer 1 (L1) utilized by HICANNs at a wafer level provides intra-wafer action potential transmission on a high density direct interconnection grid. A second one, named Layer 2 (L2), deploys the DNCs and FPGAs for synchronous, packet-based, intra- and inter-wafer communication and-compared to L1-establishes a more flexible routed network of lower density. To cope with inevitable jitter in routing delay, a time stamp is transmitted together with the address within the data packets of this network. A PC cluster that handles the mapping, configuration and control process described in Sect. 2.2 as well as the playback and recording of external stimuli to the neural network is connected to the FPGAs via multi-Gigabit Ethernet.

Activity is injected into the L1 network in the form of 6 bit serial pulse address packets by neurons that connect to the horizontal buses. Sparsely populated passive switch matrices at the intersections of horizontal and vertical buses pass the data to the vertical buses. Further sparse switch matrices connect to horizontal lines feeding synapse drivers that act as data sinks to the network. While crossing HICANN block boundaries the signals are refreshed by repeater circuits with active re-timing that are capable of driving the signals across one HICANN block. The sparseness of the switch matrices is chosen such that the repeater circuits are not overloaded while still providing maximum flexibility for implementing various neural network topologies (see Fieres et al. 2008; Schemmel et al. 2010 for more information on the underlying design decisions and analyses of the resulting limitations).

Connectivity between the HICANN blocks is established by edge connecting them in the layout. As illustrated in Fig. 5, this is only possible for eight HICANNs located within one reticle. A reticle is the largest producible unit on the wafer and no connections can be formed between reticles during standard CMOS fabrication. Wafer-scale connectivity is obtained using a post-processing method developed in the FACETS project. It offers two additional routing layers that can cover the whole wafer. By means of this technique, an inter-reticle connection pitch well below 10  $\mu$ m can be achieved which facilitates the required connectivity. Furthermore, large landing pads are formed by the post-processing that connect the wafer to the system PCB via elastomeric stripe connectors (see Fig. 2 and Schemmel et al. 2010).

These stripe connectors are used to deliver all required power to the wafer. In addition, they connect high-speed communication signals between the HICANNs and the DNCs.<sup>5</sup> This high-speed communication interface transports configuration data as well as the above-mentioned L2 data packets. L2/L1 protocol conversion is performed inside the HICANN blocks, where L2 activity can either be injected to or read from the L1 network (see Fig. 5). The transport of the L2 packets is handled by the DNCs, which also implement a time stamp- based buffering and heap-sort algorithm (Scholze et al. 2010). Together with routing logic inside the FPGAs, the DNC-FPGA L2 network fulfills the QoS<sup>6</sup> demands (Philipp et al. 2009) for spiking neural networks, i.e., a constant delay at a low pulse loss rate. This is also true for inter-wafer connections routed through Ethernet switches connected to the FPGAs.

<sup>&</sup>lt;sup>5</sup> For completeness it should be noted that also analog signals, e.g., selectable neuron membrane voltages, are transported through the stripe connectors.

<sup>&</sup>lt;sup>6</sup> Quality of service.

**Fig. 5** Communication structure on a wafer module of the FACETS wafer-scale hardware system. Neural activity is transported horizontally (*dark gray*) and vertically (*light gray*) via asynchronous L1 buses on the HICANN building blocks. Repeater circuits at the edges of these blocks allow for a distribution of the buses over the whole wafer. Off-wafer

connectivity is established by the L2 network via DNCs and FPGAs. It interfaces the L1 buses on the HICANN building blocks. Several wafer modules can be interconnected using routing functionality between the FPGAs via Ethernet switches

#### 2.1.4 Host interface

The packet communication between wafer and host computer passes through several layers: DNCs, FPGA controller boards, and a Gigabit Ethernet layer (Norris 2003) have to be traversed. As each of the 12 FPGA controller boards (see C in Fig. 2) comprises two Gigabit ports dedicated for host communication, a total bandwidth of 24 GBit/s can be achieved. Standard networking switches concentrate these links into the required number of 10GBase-LX4 (Horak 2007) upstream ports. A standard PC cluster equipped with adequate network interface cards handles the traffic. A custom design ARQ<sup>7</sup>-style (Fairhurst 2002) protocol provides a reliable communication channel between the host computer and the hardware system. The FPGA controller boards act as remote terminals for these ARQ communication channels, but also provide system control functionality.

During experiments, most communication data—basically spike events—flow directly between host computer and FPGA controller boards. In contrast to this, in the initial setup stage almost all traffic—i.e., the system configuration data is dedicated to wafer communication. In this case, the FPGA controllers act as simple transmission nodes between host computer and wafer. Both operational stages impose high demands on the communication bandwidth. The initial configuration space consumes around 50 MB (see Fig. 4). Every spike event is represented by a 15-bit time stamp and a 12-bit data field, comprising both DNC and HICANN identifiers. Thus, during an experiment approximately 1 GEvent/s can be transported to and from the host computer. At a speedup factor of  $10^4$ , the corresponding total spike rate in the biological time domain is 100 kHz per wafer.

To meet these requirements set by the hardware scale, acceleration factor and modeling constraints, a highly scalable software implementation of the communication protocol was developed (see Sect. 2.2.10 and Schilling 2010). This multi-threaded protocol stack already provides a zero-copy API<sup>8</sup> to the upper software layers.

Furthermore, to support future applications, such as interfacing the FACETS hardware system to simulated environments which provide sensor output related to motor input, low round-trip times between these components are crucial. Such classes of in-the-loop experiments demand low latency communication and high bandwidth at the same time.

#### 2.1.5 Chip-based neuromorphic system

On the development path toward the FACETS wafer-scale hardware platform, a purely chip-based neuromorphic system has been designed and built (Schemmel et al. 2006, 2007) and is in active use (Kaplan et al. 2009; Brüderle et al. 2009, 2010; Bill et al. 2010). It implements time-continuous leaky integrate-and-fire cells with conductance-based synapses and both a short-term and a long-term plasticity mechanism as described above for the wafer-scale device. Up to 16 of these ASICs, each of which provides 384 neurons and 10<sup>5</sup> configurable and plastic synaptic connections, can be operated individually or interconnected via a supporting backplane board. This board is connected via a single Gigabit Ethernet link to a host computer, through which multiple users

<sup>&</sup>lt;sup>7</sup> Automatic repeat request.

<sup>&</sup>lt;sup>8</sup> Application programming interface.

can access and use the neuromorphic devices in parallel. The possibility of remotely accessing the chips via the Internet in addition to setting up and running experiments with an available PyNN interface (see Sect. 2.2.1 and Brüderle et al. 2009) already now make this system a tool that is used for neuromorphic model exploration by users from various countries. Many circuit design strategies for the wafer-scale system are implemented for testing purposes in this chip-based device, including the STDP correlation measurements (see Sect. 2.1.2) located in every individual synapse. Basic plasticity studies supporting the design of the wafer-scale system, some of which are outlined in Sect. 2.5.3, incorporate investigations on the basis of experimental results from the chip-based devices.

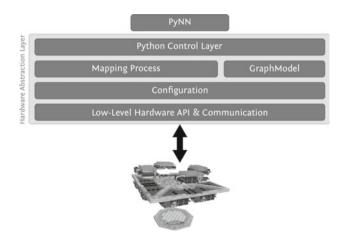

# 2.2 Software framework

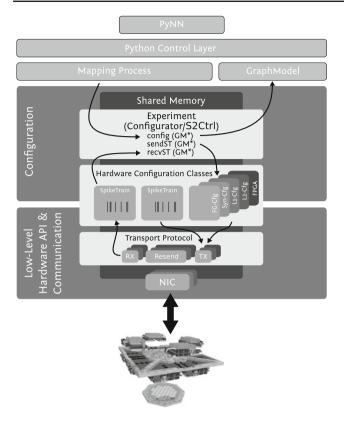

Figure 6 shows the stack of software modules that will be described in the following.

Its components seamlessly interact in performing an automated translation of arbitrary neural network experiment descriptions into appropriate data for hardware configuration and control. The same stack also automatically re-interprets the acquired hardware output into its biological interpretation. The top-level interface offered to hardware users to describe neural network setups is based on the simulator-agnostic modeling language PyNN. The concept of this approach and its advantages, especially for neuromorphic system operation, will be described in Sect. 2.2.1.

The process of mapping a PyNN description onto the configuration space of the FACETS hardware systems, includ-

**Fig. 6** Schematic of the *hardware abstraction layer*, i.e., the stack of software modules for the automated and bidirectional translation between PyNN-model descriptions and appropriate hardware configuration and control patterns. The individual modules are: a Python control layer, a mapping layer that operates on a graph-based data container (*GraphModel*), and low-level layers that deliver the generated hardware configuration patterns and control sequences via a dedicated communication protocol

ing dedicated representation formats, will be described in Sects. 2.2.2–2.2.8. Sections 2.2.9 and 2.3 focus on the mapping analysis plus its testing and optimization on the basis of an elaborate virtual version of the wafer-scale hardware system. The special performance requirements for the low-level host-to-hardware communication software and the implemented corresponding solutions are outlined in Sect. 2.2.10.

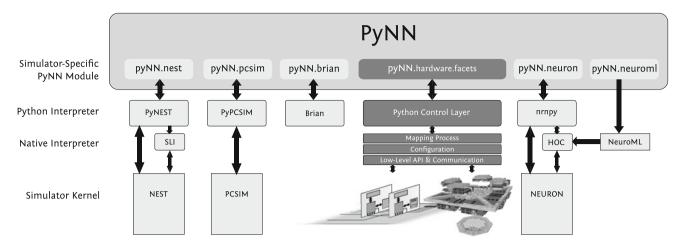

# 2.2.1 PyNN & NeuroTools

PyNN is a simulator-independent, Python-based language designed for describing spiking neural network models (Davison et al 2008). It offers functions and classes for the setup and control of experiments, and it provides standard cell models as well as standardized dimension units. PyNN supports various software simulators like NEURON (Hines and Carnevale 2006; Hines et al. 2009), NEST (Gewaltig and Diesmann 2007; Eppler et al. 2008), Brian (Goodman and Brette 2008), and PCSIM (Pecevski et al. 2009). With PyNN, which is open source and well documented, a user can set up a neural network model, run it on any of the supported back-ends without changing the code, and directly compare the results. This provides the possibility to conveniently port experiments between different simulators, to transparently share models and results, and to verify data acquired from different back-ends (see Fig. 7).

The integration of the operating software framework for the FACETS hardware system into the PyNN concept (Brüderle et al. 2009; Brüderle 2009) is a crucial aspect of the presented neuromorphic workflow. One important motivation for this approach is to create a bridge between the communities of neuromorphic engineers and neural modelers, who have been working in rather separate projects so far. The back-end agnostic concept of PyNN, now also offering the possibility to port existing experiments between the supported software simulators and the FACETS hardware system, allows to benchmark and verify the hardware model. The API of PyNN is easy to learn, especially for scientists who have already worked with software simulators. Hence, PyNN represents an optimal way to provide non-hardware experts a convenient interface to work with the FACETS neuromorphic devices. In general, PyNN interfaces to neuromorphic systems make it possible to formulate transparent tests, benchmarks and feature requests, and therefore can influence and boost biologically oriented hardware development. They might, eventually, support the establishment of such emulation devices as useful modeling tools.

On top of PyNN, a library of analysis tools called Neuro-Tools (NeuroTools 2008) is being developed, which builds upon the interface and data format standards, but also exploits the possibility to incorporate third-party Python modules, e.g., for scientific computing and plotting (Oliphant 2007; Jones et al. 2001; Langtangen 2008; Hunter 2007). Thus, for

Fig. 7 Schematic of the simulator-independent modeling language PyNN. Like various established software simulators, the FACETS neuromorphic hardware systems have been integrated into the PyNN unification and standardization concept

all supported software simulators and for the FACETS neuromorphic hardware systems, all stages of neural modeling experiments—description, execution, result storage, analysis, and plotting—can be performed from within the PyNN and NeuroTools framework.

2.2.1.1 Simulations as reference for translation and calibration The hardware-specific PyNN approach incorporates quantitative bidirectional translation methods between the neuromorphic system dynamics and the biological domain, both in terms of electrical variables and the different time domains. This translation incorporates calibration routines that minimize the impact of transistor-level fixed-pattern noise on the behavior of neural and synaptic circuits. The translation and calibration scheme developed for the FAC-ETS hardware systems directly involves reference software simulations for the biologically relevant gauging of hardware parameters, heavily exploiting the PyNN paradigm of unified setup descriptions. Section 2.2.7 provides more details on this.

# 2.2.2 Mapping process

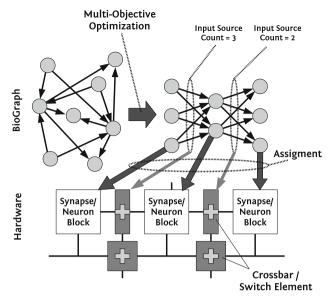

The mapping process determines a valid routing network configuration and parameter value set as initial setup data for the FACETS hardware system. This takes into account topology constraints between hardware blocks such as connectivity, connection counts, priorities, and distances as well as source/target counts. Figure 8 depicts the single steps of the mapping process as described by Ehrlich et al. (2010).

The mapping is accomplished in the three main steps of *Placement, Routing,* and *Parameter Transformation & Calibration,* with an appropriate *Pre-* and *PostProcessing* of the configuration data. As the first three main steps are explained in more detail in the following, we will shortly summarize the functionality of the remaining parts.

**Fig. 8** Mapping PyNN neural network model descriptions onto the configuration space of the wafer-scale hardware system. The three main processing steps, all operating on one unified data container (Graph-Model), are **a** the *placing* of neurons onto the available circuitry, **b** the realization of synaptic connections by appropriately configuring the available *routing* infrastructure on the device, and **c** the transformation of neuron and synapse parameters into corresponding parameter values offered by the highly configurable device. The latter step can involve calibration data to tune individual sub-circuits such that the effect of unavoidable transistor-level variations onto the mapped models is minimized

Starting with a neural architecture defined via PyNN, the first mapping step of *PreProcessing* reads in a description of the hardware (see Sect. 2.2.3), described using the novel

query language *GMPath* (see Sect. 2.2.4). It sets up an internal representation for both the hardware and the biological model in the form of a directed graph called *Graph Model* (see Sect. 2.2.4). Optionally, a so-called *PreMapping* netlist of the biological model can be streamed out into a file. Following placement and routing, the same applies for the *PostProcessing* with a *PostMapping* netlist, which includes the possibility to obtain a PyNN script that represents the (possibly distorted) network ultimately realized on the hardware back-end.

The individual steps of the process are automatically initiated and partly controllable via the PyNN module for the FACETS hardware system. Furthermore a stand-alone software named *GraViTo* is provided for the analysis of the mapping results (see Sect. 2.2.9).

# 2.2.3 Internal hardware description

Prior to the mapping process, we have to define the hardware in an abstract manner. For this purpose, we utilize the path language *GMPath* to set up an appropriate GraphModel (both described in Sect. 2.2.4) as a versatile internal representation.

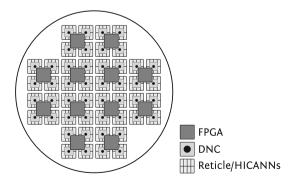

In Fig. 9, a FACETS wafer-scale hardware setup—also applied in Ehrlich et al. (2010)—is illustrated.

As described in Sect. 2.1, the fundamental layer of the FACETS wafer-scale hardware is an array of reticles shown as light gray squares, housing the HICANN circuitry that implements neural functionality, with a second layer of DNCs above. The third and topmost layer represents a regular grid of FPGAs, colored dark gray.

### 2.2.4 The GraphModel container

A data model called *GraphModel* (Wendt et al. 2008) represents both the targeted biological and the configurable hardware structure within the mapping software. It can be characterized as a hierarchical hyper graph and consists of vertices (data objects) and edges (relationships between the

Fig. 9 Example FACETS wafer-scale hardware setup from Ehrlich et al. (2010): 12 FPGAs control 48 DNCs, which are connected to 384 HICANN ASICs

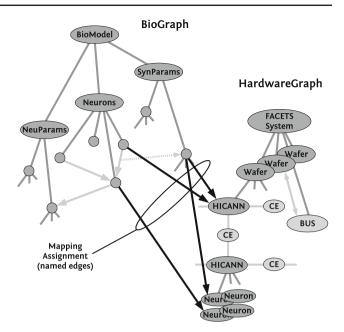

Fig. 10 A simplified example of two graph models, assigning neural elements to hardware components

vertices). A vertex contains a single data value. An edge can be one of the following types:

| hierarchical: | models a parent-child relationship, structuring |

|---------------|-------------------------------------------------|

|               | the model.                                      |

| named:        | forms a directed and named relation between     |

|               | any two vertices in the model.                  |

| hyper:        | assigns a vertex to a named edge, characteriz-  |

|               | ing the edge in more detail.                    |

|               |                                                 |

The major advantage of this graph approach are the implementation convenience and efficiency as well as the flexibility to achieve the complex requirements from both the biological and the hardware model. Due to the structure of the graph model it can be easily (de-)serialized, providing save and restore functionality. Via the path-based query-language *GMPath* (Wendt et al. 2010) information can be dynamically retrieved from and stored to the models. The GraphModel is used to store all information during the configuration process, i.e., the models themselves, the mapping, routing and parameter transformation algorithms data and their results.

Figure 10 shows the graph model representation of a biological network (called *BioGraph*) and its hardware representation (called *HardwareGraph*), connecting elements via named edges after a placement step.

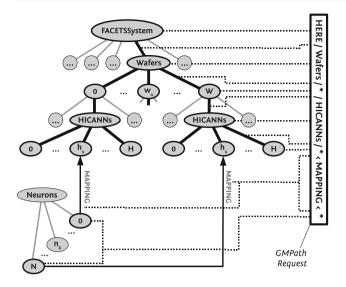

2.2.4.1 The Query Language GMPath To retrieve information from and propagate data to the graph models, the path-based query language GMPath was developed, providing a universal interface for placing and routing algorithms as well as for configuration, visualization, and analysis tools

Fig. 11 An example GMPath request to retrieve all assigned neurons of the biological model

(Wendt et al. 2010). Based on so-called navigational steps, a path request can enter the model at any point (node or edge) and addresses iteratively the logical environment by

- shifting the focus hierarchically up- or downward.

- shifting the focus back and forth along edges.

- filtering according names.

- concatenating sub-queries.

The results are lists of nodes or edges and serve the requesting software as model information input. Because of its string-based format and the ability to address nodes or edges unambiguously, the queries can be created conveniently and dynamically at runtime and can be used to extend and modify the models.

Figure 11 exemplarily shows subsequent navigational steps of an executed path request, which enters the abstract hardware model at its root, addresses all existing HICANN nodes and finally follows incoming mapping edges to their origins, the neurons of the biological model.

# 2.2.5 Neuron placement

The process of assigning neural elements like neurons, synapses or their parameters to distinct hardware elements is called *placement*. It can be characterized as a multi-objective optimization problem, the solution of which significantly influences the overall mapping results. Typical algorithmic approaches create clusters of cells with common properties that are mapped to the same HICANN building blocks. Possible optimization objectives are:

- minimize neural input/output variability cluster-wise.

- minimize neural connection count cluster-wise.

Fig. 12 An example placement, divided into an optimization and assignment step

- comply with parameter limitations.

- comply with cluster capacities (neural capacity of hardware elements).

- minimize routing distances.

In order to achieve these objectives with user-defined weightings in acceptable computation time, a force-based optimization heuristic was developed. This algorithm balances modeled *forces* (special implementations of the optimization objectives) in an *n*-dimensional space until an equilibrium is reached and a final separation step assigns data objects to clusters with affine properties. Despite this problem being NP-complete, significantly improved results can be found with this algorithm in an acceptable computation time, as compared to a fast random placement.

Figure 12 illustrates a placement process, divided into an optimization step, which sorts the given biological network for optimal hardware utilization with regard to the input source variability, and an assignment step, defining the physical realization of neural elements on the hardware system.

# 2.2.6 Connection routing

The routing step allocates and configures the hardware resources for establishing the synaptic connections in the already placed BioGraph. Given the fixed amount of available resources it is not evident a priori whether arbitrary network topologies are always perfectly reproducible.

Synaptic connections can in principle be established via the L1 and L2 infrastructure (see Sect. 2.1.3). In the approach described here, all intra-wafer connectivity is routed exclusively on L1. The L2 network is reserved for inter-wafer connections in a multi-wafer system.

The intra-wafer routing algorithms were developed in close cooperation with the wafer design (Fieres et al. 2008). Some hard-wired features of the L1 infrastructure are thus laid out to optimally suit the routing requirements. The routing itself is performed in two stages. The first stage establishes connections on a HICANN-to-HICANN level via the horizontal and vertical L1 buses, mainly by configuring the bus repeaters and sparse crossbars (see Fig. 5). In the second stage, the signals are routed from the vertical L1 bus lanes into the synapse arrays via the sparse switch matrices, the synapse drivers and the address decoders of the synapses, the latter not being shown in Fig. 5.

The algorithms were proven in various test scenarios: homogeneous randomly connected networks with up to 16,000 neurons, locally connected networks (according to Tao et al. 2004) as well as a model of a cortical column (following Binzegger et al. 2004; Kremkow et al. 2007) with 10,000 neurons. It turns out that in typical cases only a small amount of unrouted connections must be accepted, mainly due to limited resources in the second routing stage. However, it was also shown that by decreasing the density of the neuron placing the routing can be generally facilitated, at the expense of a larger portion of idle hardware synapses.

The routing algorithms proved to be also applicable for the benchmarks described later in this publication, see Sect. 2.4 and Ehrlich et al. (2010).

#### 2.2.7 Parameter transformation

The parameter transformation maps parameters of given neuron and synapse models into the hardware parameter space. It is performed HICANN-wise. Biological data is first acquired from the so-called *BioGraph* of the GraphModel (see Sect. 2.2.4) and then transformed into a hardware configuration, which is stored back into the *HardwareGraph*. For an adequate biology-to-hardware translation several constraints have to be considered, such as hardware imperfections and shared or correlated parameters in the microchip.

For the membrane circuits, a two-step procedure was developed to translate the 18 biological parameters from the PyNN description to the 24 electrical parameters of the HIC-ANN building block. The first step is to scale the biological neuron model parameters in terms of time and voltage. At this stage, the desired acceleration factor is chosen and applied to the two time constants of the neuron model. Then, the biological voltage parameters are transformed to match the voltage levels of the HICANN building block. The second step is to translate those intermediate values to appropriate hardware parameters. For this purpose, each part of the membrane circuit was characterized in transistor-level

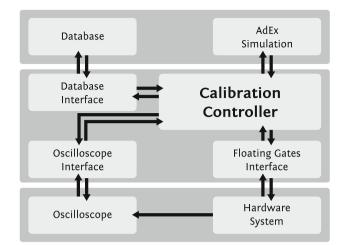

Fig. 13 Architecture of the calibration software. The main component, the calibration controller, executes the calibration algorithms and communicates with the hardware, the oscilloscope and the database via dedicated interfaces. The calibration software also incorporates an AdEx model simulator to compare software and hardware results

simulations, which were used to establish the translation functions between the scaled AdEx parameters and their hardware

counterparts.

However, due to transistor size mismatch in the hardware, these translation functions are expected to differ from neuron to neuron. A calibration software has been developed to automatically parameterize these translation functions for each neuron. For each neuron model parameter, the software will send a spectrum of values to the HICANN building block, and measure the resulting membrane potentials of the current cell. It will then deduce the corresponding AdEx parameters from these measurements, and store the value pairs into a database. After a given number of measurement points, the algorithm will compute the relation between the hardware parameters sent to the floating gates and the AdEx parameters, and store this function into the database. Figure 13 illustrates the calibration software architecture.

Once the calibration step is done, the database can be used to automatically convert a set of biological neuron parameters to their hardware counterparts, allowing on-the-fly conversion of neuron parameters for the wafer-scale hardware system.

Concerning the synapses, there are mainly two restrictions ensuing from the chip design: 256 synapses of the same row share the maximal conductance  $g_{max}$  and the short-term plasticity mechanism, and weights are restricted to a 4-bit resolution. By averaging over all active synapses, the transformation algorithm determines  $g_{max}$  and sets the digital weights accordingly, using *stochastic rounding* to avoid systematic errors.

# 2.2.8 Application of the mapping flow onto the FACETS chip-based system

In order to further demonstrate the versatility of the Graph-Model-based mapping flow introduced in Sect. 2.2.4, we briefly outline the adoption of this procedure to the operation of the FACETS chip-based systems (see Sect. 2.1.5). This integration avoids code redundancy by unifying the previously independent PyNN back-ends and allows to map neural architectures onto inter-connected chips beyond single-chip boundaries (Jeltsch 2010). Due to the flexible design of the mapping framework, the translation of the PyNN description into the biological graph representation (see Sect. 2.2.2) and the placing of biological neurons onto their hardware counterparts (see Sect. 2.2.5) could be kept completely unchanged. Necessary extensions were limited to the development of a new internal hardware model that captures all features of the chip-based system as well as adapted versions of the routing and the parameter translation (described in Sects. 2.2.6 and 2.2.7, respectively) to match the different network topology and electrical parameters. Together with the low-level event distribution network established by Friedmann (2009), neural network models can now be scaled to multiple chips.

# 2.2.9 Mapping analysis and visualization

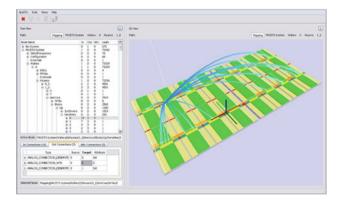

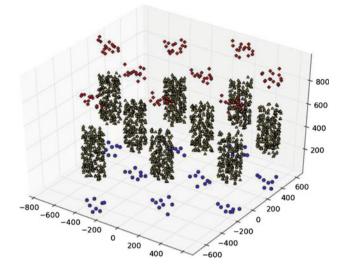

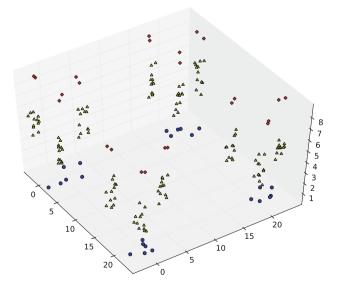

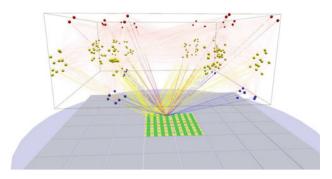

The application *Graph Visualization Tool—GraViTo* as described by Ehrlich et al. (2010) aids in analyzing the mapping results. GraViTo, as shown in Fig. 14, integrates several modules that display graph models in textual and graphical form and gathers statistical data. One can selectively access single nodes inside the data structure and visualize their context, dependencies and relations with other nodes in the system.

The example of the GraViTo views shows a *tree view* on the left which is utilized to browse the hierarchical structure of the graph model and examine contents and connections of individual nodes. The *3-D view* on the right provides a

Fig. 14 Screenshot of the GraViTo application

virtual representation of the FACETS wafer-scale hardware system for interactively browsing its architecture and configuration. It also provides a global overview over the single hardware components and the networks they form. Various statistics such as histograms for utilization of the crossbars or the synaptic connection lengths are gathered and can be displayed.

Another option for a systematic mapping analysis arises from the previously mentioned possibility to re-translate the configured HardwareGraph contents via the mapping edges through the BioGraph into a *PostMapping* PyNN script. This script intrinsically contains all model distortions caused by the mapping process, e.g., lost synapses and discretized or clipped parameter values. Exploiting the PyNN concept, it can then be directly evaluated with a software simulator to extract possible functional consequences of the structural distortions, avoiding interferences with other effects like on-wafer communication bandwidth limitations.

# 2.2.10 Hardware low-level interfacing

A specialized protocol of the class of *selective*  $ARQ^9$  *protocols* is used to provide a fast and reliable communication channel with the neuromorphic hardware device. In the OSI model<sup>10</sup> this corresponds to the transport layer.

Configuration and experimental data is bidirectionally transmitted via two 10 GBit/s Ethernet links per FPGA. In order to handle up to 2 GByte/s of traffic while keeping the load of the host computer as low as possible, several software techniques have been applied to the protocol implementation. Various features of existing transport protocols, notably TCP, have been implemented, including congestion avoidance, RTT<sup>11</sup> estimation and packet routing to keep the connection in a stable and bandwidth maximizing regime.

In matters of performance the framework is divided into three mainly independent processing *threads* (see Fig. 15, receiver thread *RX*, sender thread *TX*, and *resend* thread) to exploit the speed-up in execution of modern multiprocessor systems. Performance critical data, e.g., spike data can be placed in *shared memory* and passed to and from the hardware abstraction layers such as to avoid unnecessary copying. These shared data structures have to be protected against concurrent accesses which imposes an additional overhead in processing time. Thus, to keep the number of system calls and context switches small, access to data located in shared memory is protected by means of custom built user-space fencing and locking methods.

A purely software-stack-based test has been developed that establishes a reliable ARQ connection between two host

<sup>&</sup>lt;sup>9</sup> Automatic repeat request.

<sup>&</sup>lt;sup>10</sup> Open systems interconnection model.

<sup>&</sup>lt;sup>11</sup> Round-trip time.

**Fig. 15** Configuration and runtime control steps in the hardware abstraction layer: the *Experiment* module acquires the configuration data from the Mapping Process (see Sect. 2.2.2 and Fig. 8), generates a hardware-specific representation of this data and triggers the transfer to the hardware system

computers via 10 Gigabit Ethernet. With a hardware-specific version of this protocol, i.e., with frame sizing and protocol window size, it delivers 10 GBit/s (Schilling 2010).

# 2.3 Virtual hardware

An executable specification of the FACETS wafer-scale hardware system serves as a versatile tool not only during device design and optimization, but also as a test bench for all involved software layers. It is a functional model that can be used to explore the behavior and characteristics of the real wafer-scale system in its final phase of development.

# 2.3.1 Implementation

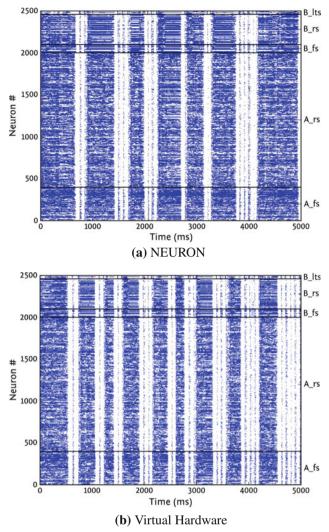

The so-called *virtual hardware* is a detailed simulation of the final hardware platform and has been implemented in C++/SystemC (Vogginger 2010). The virtual hardware replicates its physical counterpart in all aspects regarding functionality and configuration space. Every module of the real hardware has its functional counterpart in the virtual device, where especially the interface and communication structures accurately correspond to the physical system. It implements all analog and mixed-signal modules such as AdEx neurons and dynamic synapses (depressing and facilitating), as well as all units responsible for L1 and L2 routing. Compared to analog and RTL<sup>12</sup> hardware simulations, this model is tuned toward simulation speed using behavioral models of all relevant functional components. However, it is possible to replace individual modules by more sophisticated models, all the way down to simulating single wires on the chip.

The current implementation of the virtual hardware differs from the real hardware system in several aspects, most of them meeting efficiency considerations. The executable system specification is not operated from a host PC but directly from higher software layers, such that the host-to-system communication is not simulated. Furthermore, the configuration of the HICANN building block and its components is not conducted via packets received from L2, as the software implementation of the used protocol is still under development. Instead, every HICANN obtains its configuration via direct access to the GraphModel (see Sect. 2.2.4). Despite these differences the virtual hardware remains a proper replica of the FACETS wafer-scale system providing equal functionality while not suffering from hardware-specific constraints like transistor-level imperfections from the manufacturing process.

#### 2.3.2 Analysis and verification based on virtual hardware

With its functionality and flexibility, the virtual hardware is an essential tool for the development of the software framework operating the FACETS wafer-scale hardware This includes the PyNN interface and the placement, routing and parameter transformation algorithms (see Sects. 2.2.1 and 2.2.2), which can already be tested and verified despite the real hardware not yet being available. The development of a hardware system, which shall be useful in a neural modeling context, can be strongly supported already during its design phase by determining constraints inherent to the system architecture, such as communication bottlenecks or the effect of shared and digitized parameters. Their influence can be evaluated without the interference of hardware imperfections or a missing calibration. Such studies build the basis for improvements in the hardware design or, if possible, the development of software-based corrections. The virtual hardware can be used from PyNN-like any other supported software simulator, thereby also offering an early modeler's perspective onto the capabilities of the future FACETS waferscale platform. Any PyNN-model, in particular the benchmark models described in Sect. 2.4, can be applied to this setup. Their output can later be analyzed and compared to reference software simulations, revealing the impact of

<sup>&</sup>lt;sup>12</sup> Register transfer level.

hardware constraints onto the model behavior, e.g., the loss of certain synaptic connections during the mapping process.

# 2.4 Benchmark model library

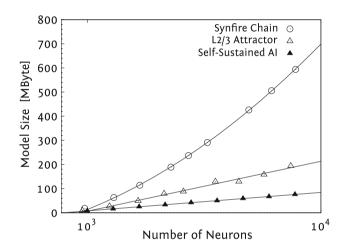

We will now present a set of experiments that serve as benchmarks for the previously described mapping process. The setups are implemented in PyNN and have been contributed by FACETS project partners. They not only cover various computational aspects like memory, pattern recognition, robust information propagation in networks or dynamic switching between different functional modes, but also very different structural characteristics.

#### 2.4.1 Layer 2/3 attractor memory model

The model used here remains faithful to the model of neocortical layers 2/3 in Lundqvist et al. (2006), and in doing so retains the modularity that is the key aspect of this architecture (Lundqvist et al. 2010). It represents a patch of cortex arranged on a hexagonal topology of  $N_{\rm HC}$  hypercolumns each separated by 500 µm, in agreement with data from cat cerebral cortex recordings. Each hypercolumn is further subdivided into  $N_{\rm MC}$  minicolumns, and various estimates suggest that there are about 100 minicolumns bundled into a hypercolumn (Mountcastle 1997; Buxhoeveden and Casanova 2002). For the default version of the Layer 2/3 Attractor Memory benchmark model, a total number of  $N_{\rm HC} = 9$  hypercolumns and a sub-sampling of  $N_{\rm MC} = 8$  minicolumns per hypercolumn has been used.

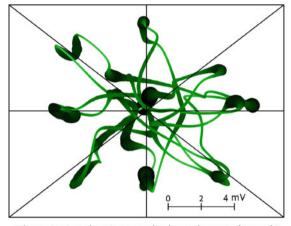

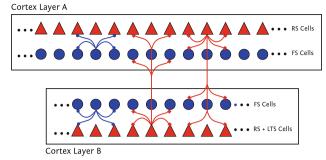

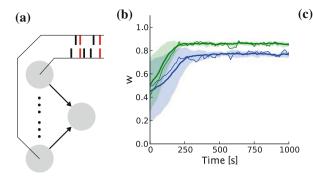

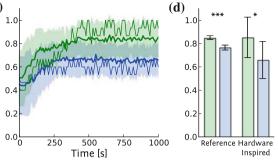

The arrangement of the cells in the local microcircuit together with connection probabilities is shown in Fig. 16a.

In the default variant of the model, each minicolumn consists of 30 pyramidal cells densely connected to other pyramidal cells in the same minicolumn ( $P_{\rm PYR-PYR} = 25\%$ ) and two regular spiking non pyramidal (RSNP) cells that project to  $P_{\text{RSNP-PYR}} = 70\%$  of the pyramidal cells. Each hypercolumn has eight basket cells, with each pyramidal cell in a minicolumn targeting  $P_{\text{PYR-BAS}} = 70\%$  of neighboring basket cells, and each basket cell targeting  $P_{\text{BAS-PYR}} = 70\%$  of neighboring pyramidal cells. The extent of basket cell inhibition is limited to its home-hypercolumn (Douglas and Martin 2004). Apart from these local connections, pyramidal cells located in different hypercolumns are also connected globally ( $P_{\text{MC-MC}} = 17\%$ ). The cartoon in Fig. 16b shows how the minicolumns in different hypercolumns, denoted by dashed lines, are connected. We developed methods to scale this architecture up or down by means of both  $N_{\rm HC}$  and  $N_{\rm MC}$  without losing its functionality. They are described in Sect. 2.5.1 and experimentally applied in Sect. 3.2.

Thus, a set of mutually exciting minicolumns distributed over different hypercolumns represents a stored pattern or an

Fig. 16 Schematic detailing the network arrangement and all the excitatory and inhibitory pathways between different cell groups and their connection densities in the L2/3 Attractor Memory network model. **a** Connectivity densities of the sub-sampled network model. See the text for further description. **b** Cartoon of a network with nine hypercolumns (HC). Each hypercolumn has eight circularly arranged minicolumn (MC). The large disc at the center of each hypercolumn represents a population of basket cells. *Dashed lines* show mutually exciting minicolumns that are distributed over different hypercolumns, forming a pattern

attractor of the network dynamics. RSNP cells in a minicolumn also receive long-range excitation. They are excited by distant pyramidal cells, given their home minicolumn is not part of the active pattern, thus inhibiting the pyramidal cells in the minicolumn. In this network, we can store as many patterns as the number of minicolumns in a hypercolumn, but by allowing for overlapping memory patterns the number of stored patterns can be increased significantly.

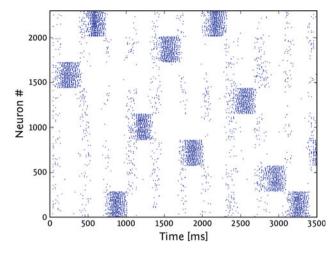

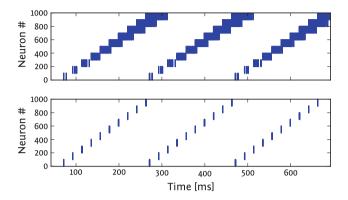

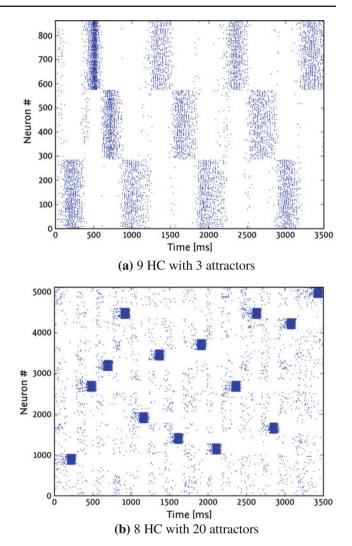

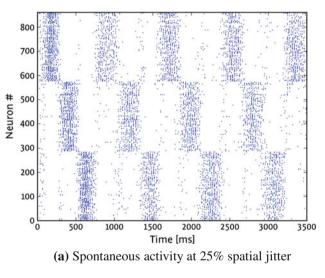

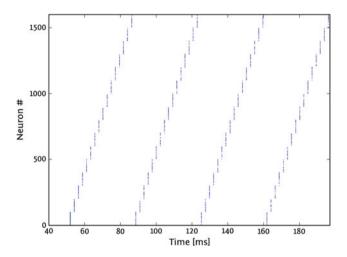

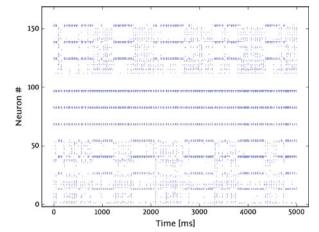

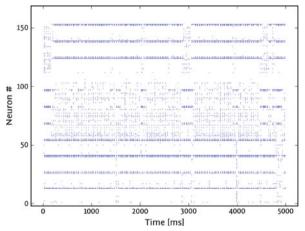

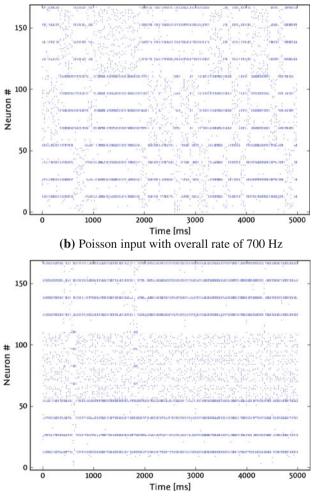

Figure 17 shows a raster plot of the activity of the network, when all pyramidal cells are excited by individual Poisson inputs of the same rate.

Whenever an attractor becomes stronger than the others (which happens randomly), it completely suppresses their activity for a short period of time.

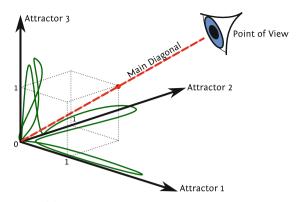

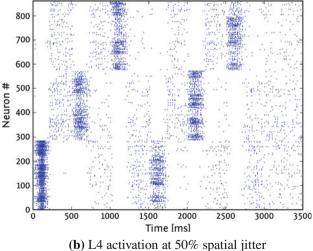

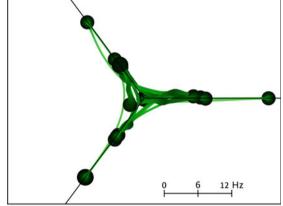

Pyramidal cells in an active attractor are in a so-called UP-state, where their average membrane potential is a few mV above its rest value. When plotting the trajectory of the system in potential space, with each axis representing the average membrane potential of all neurons inside an attractor, a projection along the main diagonal (the line which is

Fig. 17 Raster plot of characteristic activity of an L2/3 Attractor Memory network with nine hypercolumns and eight attractors

equidistant to all axes) will yield a typical star-like pattern (see Fig. 18).

The synaptic plasticity mechanisms are chosen such as to prevent a single attractor from becoming persistently active. Excitatory-to-excitatory synapses are modeled as depressing, which weakens the mutual activation of active pyramidal cells in time. In addition, the neurons feature an adaptation mechanism, which suppresses prolonged firing. Both mechanisms have the effect of weakening attractors over time, such that, in contrast to a classic WTA network, also weaker patterns may become active at times.

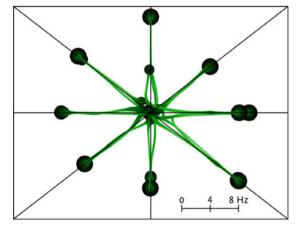

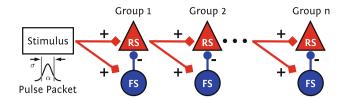

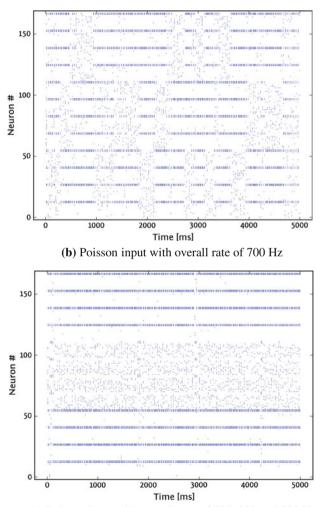

# 2.4.2 Synfire chains

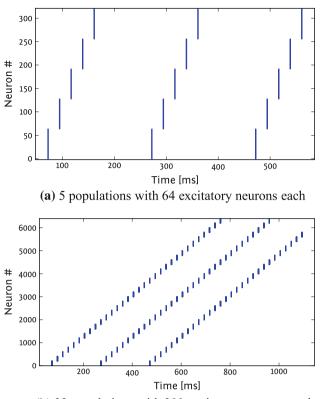

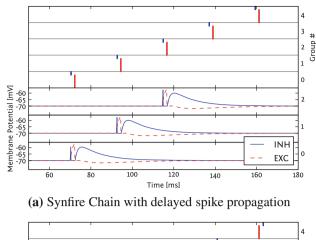

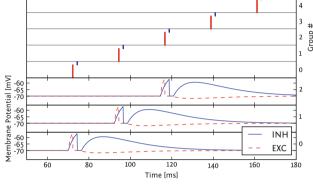

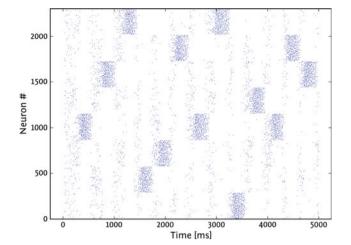

Similar to classical Synfire Chain models (Diesmann et al. 1999; Aviel et al. 2003; Kumar et al. 2008, 2010), the version chosen as a mapping benchmark consists of a chain of neuron groups connected in a feedforward fashion, with a certain delay in between. This allows spiking activity to propagate along the chain in a given direction (see Fig. 19). In addition to this, the benchmark Synfire Chain model implements feedforward inhibition by subdividing each group into a RS, excitatory (80%) and a fast spiking (FS), inhibitory (20%) population (Kremkow et al. 2010a,b). Inhibitory cells are also activated by feedforward projections of excitatory cells from the previous group, but project only locally onto the excitatory population of the same group with a small delay. This allows a fine control over the duration of spiking in a single group and prevents temporal broadening of the signal as it gets passed down along the chain. In the original model of Kremkow et al. (2010b), a Synfire Chain group consists of 100 RS and 25 FS cells. Every cell, RS or FS, receives a total of 60 excitatory inputs from the previous RS population. In addition, every RS cell receives input from all 25 inhibitory neurons of the FS population within its own group.

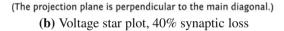

(a) Phase space trajectory projection

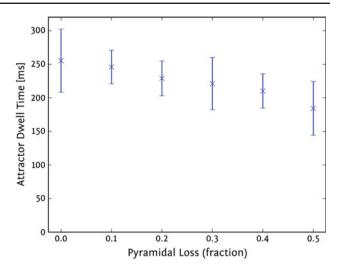

(The projection plane is perpendicular to the main diagonal.)

(b) Mean voltage trajectory

(The projection plane is perpendicular to the main diagonal.)

# (c) Mean rate trajectory

Fig. 18 a Construction of phase space projection plots as shown e.g., in **b** and **c**: the trajectory in an *n*-dimensional phase space (here: n = 3) is projected to a hyper-plane perpendicular to the main diagonal. **b** Trajectory projection of the attractor network state evolving in eightdimensional mean voltage and **c** mean rate phase space. Axis values represent the projected offset from a base value, which is the neuron resting potential (in mV) for the voltage traces and 0Hz for the rate traces. The curve becomes thicker and darker as the phase space velocity decreases

Fig. 19 Schematic of the Synfire Chain benchmark model

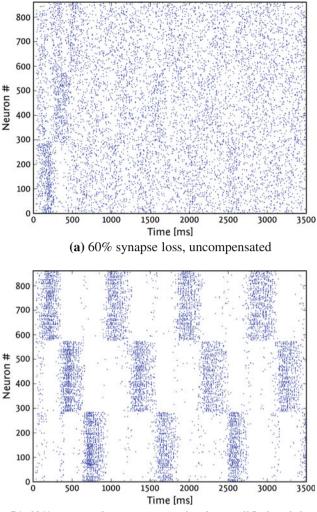

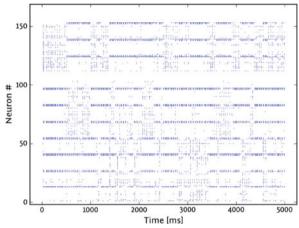

Fig. 20 Raster plot of characteristic RS activity of the Synfire Chain without (*top*) and with (*bottom*) feedforward inhibition. Note the constant spike packet width in case of the active feedforward inhibition mechanism

The inhibition is tuned such that every excitatory neuron gets to spike exactly once upon activation (see Figs. 19, 20).

Methods to scale the size of this model up or down are available and described in Sect. 2.5.1. Different architecture sizes are used to benchmark the quality of the previously described mapping process. See Sect. 3.3 for evaluation data based on scaled benchmark models.

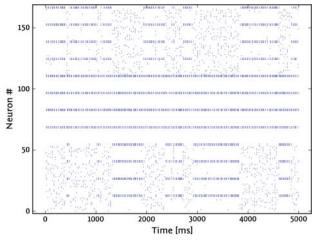

#### 2.4.3 Self-sustained AI states

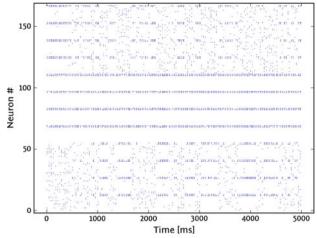

Randomly connected networks of integrate-and-fire neurons are known to display asynchronous irregular (AI) activity states, where neurons discharge with a high level of irregularity, similar to stochastic processes, and with a low level of synchrony (Brunel 2000). These states were also found in various other network models, including those using conductance-based (Vogels and Abbott 2005) and nonlinear integrate-and-fire neuron models (Destexhe 2009). They were shown to have properties very similar to the discharge patterns observed in awake animals (El Boustani et al. 2007). As cortical neurons are characterized by nonlinear intrinsic properties (Connors and Gutnick 1990), our choice of an AI state benchmark is based on the AdEx neuron model. These nonlinear IF cells are implemented in the FACETS waferscale hardware (see Sect. 2.1.2) and reproduce several cell classes observed experimentally in cortex and thalamus (see Destexhe 2009).

Fig. 21 Schematic of the self-sustained AI states benchmark model. It consists of two cortical layers A and B. Every layer has an excitatory and an inhibitory population, each of which contains certain sets of cell types (RS, FS, and LTS) that determine the network dynamics (see text for details). The excitatory populations project onto every other population, while the inhibitory populations only act within their layer

The particularity of the AI benchmark model is that it allows testing the influence of the various cell classes on the genesis of AI states by varying the different cellular properties. The model considers the most prominent cell classes in cerebral cortex, such as the *RS* cell, the *FS* cell, the *lowthreshold spike* (LTS) cell, and the *bursting* cells of the thalamus. It was found that randomly connected networks of RS and FS cells with conductance-based synaptic interactions can sustain AI states, but only if the adaptation currents (typical of RS cells) are not too strong. With strong adaptation, the network cannot sustain AI states.

To the contrary, adding another cell class characterized by rebound responses (the LTS cell) greatly enhanced the robustness of AI states, and networks as small as about 100 neurons can self-sustain AI states with a proportion of 5% of LTS cells. Interestingly, if two of such networks (one with strong adaptation, another one with LTS cells) are reciprocally connected, the resulting two-layer network can generate alternating periods of activity and silences. This pattern is very similar to the Up- and Down-states observed in cortical activity during slow-wave sleep (Steriade 2003). Reducing the adaptation leads to sustained AI states, and is reminiscent of the transition from sleep to wakefulness, a sort of "wakening" of the network. In the context of this article, we use two variants of such networks as benchmarks: First, a network of RS, FS, and LTS cells as a minimal model of AI states. Second, a two-layer cortical network displaying Upand Down-states. The latter is depicted in Fig. 21.

Also, this model can be scaled up and down in its size in order to benchmark the PyNN-to-hardware mapping process. In its default version, layer A consists of 1,600 excitatory RS and 400 inhibitory FS cells. Layer B contains 400 excitatory neurons, 90% of which are RS and 10% of which are LTS type, as well as 100 inhibitory FS cells. Within a single layer the connection probability is 2% for a network size of 2,000 cells. For smaller networks as for layer B the connection probability is rescaled inversely to the network size. The inter-layer connectivity is excitatory only and has a connection probability of 1%.

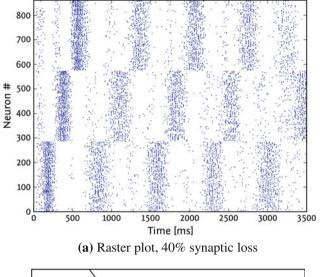

# 2.5 Analysis based on software simulations

Compared to pure software simulators, dedicated neuromorphic hardware suffers more from limitations and imperfections, which may either directly distort the morphology of the emulated network or influence its dynamics in more subtle ways. On one hand, physical limitations such as size and number of implemented circuits or communication bandwidth impose rather inflexible constraints on parameters such as number of neurons and synapses or the amount of accessible data. On the other hand, as VLSI hardware is, inevitably, subject to manufacturing process variations, individual circuits have varying characteristics, which can only be compensated by calibration to a certain degree. As all these effects influence the dynamics of an emulated network simultaneously, it is usually very difficult to identify the connection between an individual cause and its effect. The most straightforward solution is to artificially impose individual hardware-specific distortions on software simulations, identify their impact on the network's dynamics and find, if possible, suitable compensation mechanisms.

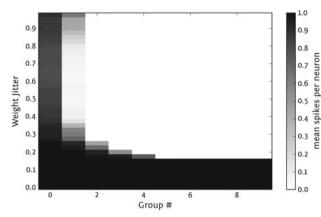

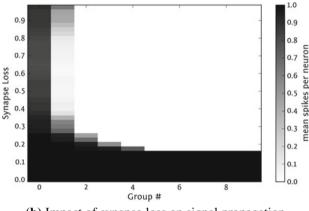

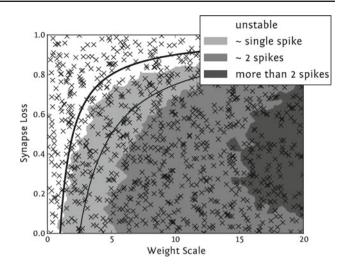

#### 2.5.1 Network scaling